# **ISCAS 2005**

### Performance Model for Inter-chip Busses Considering Bandwidth and Cost

Authors:

**Brock J. LaMeres, University of Colorado**

Sunil P. Khatri Texas A&M University

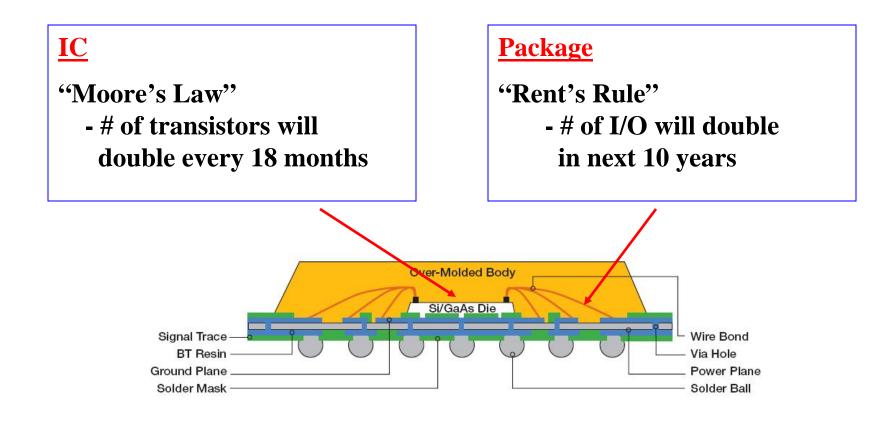

Transistor Technology is Faster than Package Technology

### **1) Supply Bounce**

• Switching current through inductive packaging induces voltage:

$$V_{bnc} = L \cdot \left(\frac{di}{dt}\right)$$

L = Inductance of pwr/gnd pin that current is being switched through.

• Multiple Signals Switching Increase the Problem:

$$V_{bnc} = L \cdot \sum_{i}^{n} \left( \frac{di}{dt} \right)$$

n = # of drivers

sharing the power/gnd

pin (L).

- 2) Pin-to-Pin Coupling

- Switching Signals Couple Voltage onto Neighbors:

$$V_{couple} = M_{1k} \cdot \left(\frac{di_k}{dt}\right)$$

M = Mutual Inductance between package interconnects.

• Multiple Signals Switching Increase the Problem:

$$V_{couple} = \sum_{1}^{k} M_{1k} \cdot \left(\frac{di_{k}}{dt}\right)$$

### • Aggressive Package Design will Reduce Inductance

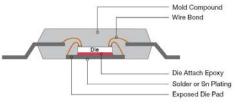

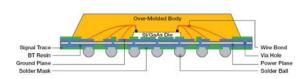

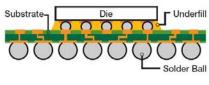

Die

0 0 0 0 0

- Underfill

Solder Ball

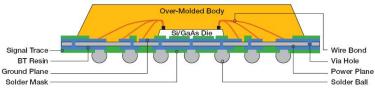

**BGA – Wire Bond** :

$$3.7nH \rightarrow $0.34$$

/ pin

• But is Expensive

Substrate

- 95% of VLSI design-starts are wire-bond

• Bus Parameters

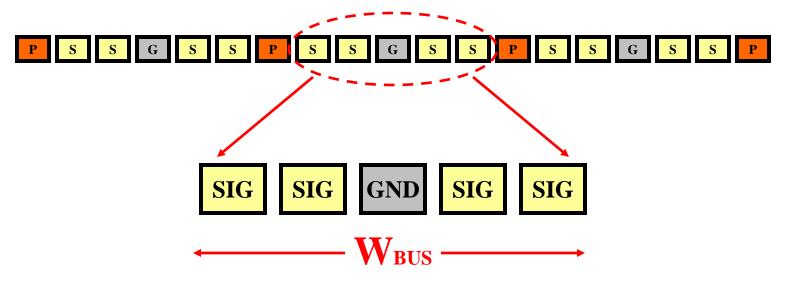

### **W**<sub>BUS</sub> : # of Signals Per Bus Segment of Interest

• Bus Parameters

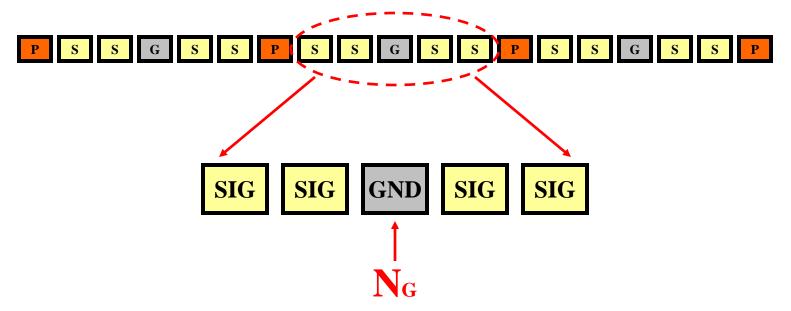

**N**<sub>G</sub> : # of Grounds Per Bus Segment of Interest

• Bus Parameters

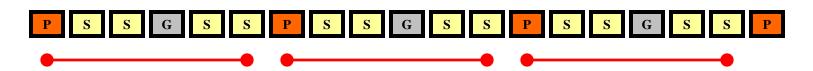

**Repetitive Pattern of Signal, Power, and Ground Pins**

# **SPG :** (# of Signals) : (# of PWR's) : (# of GND's)

### **SPR : SPG Ratio**

• Bus Performance Description

• Bus Performance Description

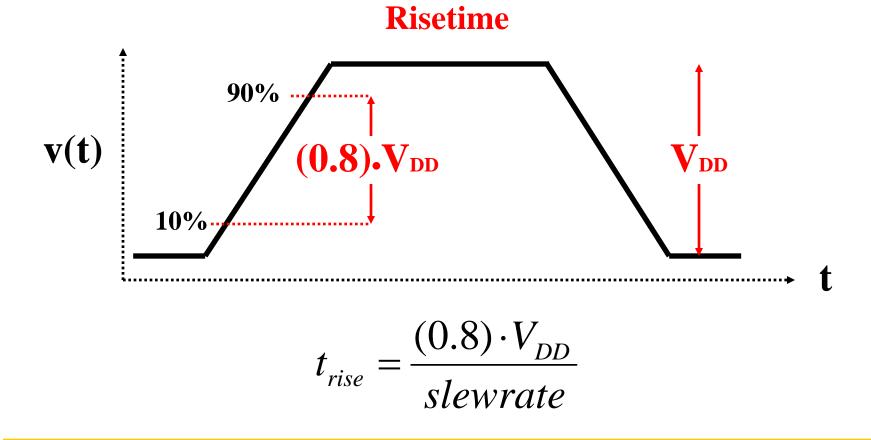

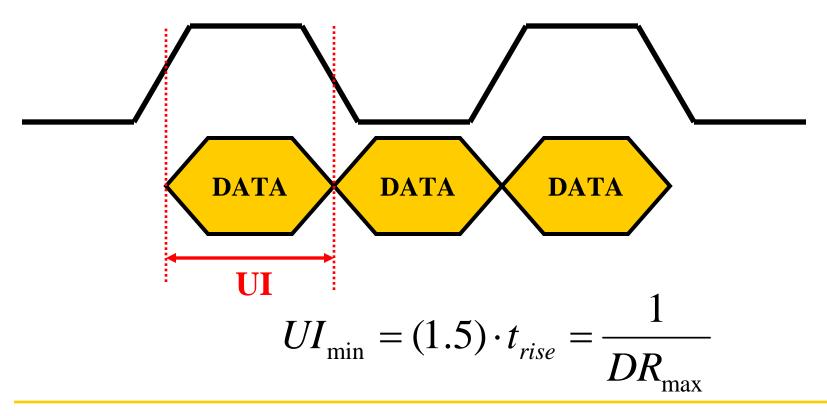

**Minimum Unit Interval**

• Bus Performance Description

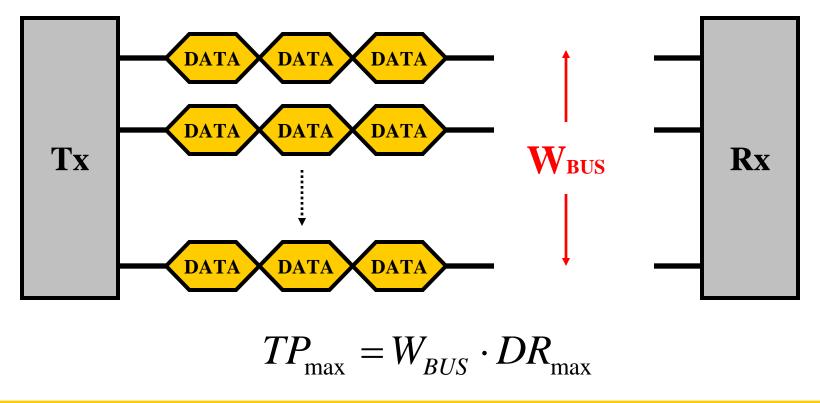

**Bus Throughput**

• Bus Performance Limits

• Model Development

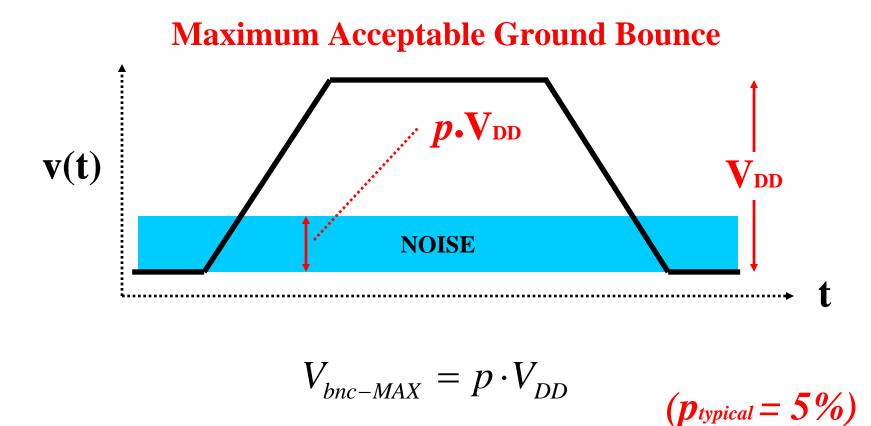

### **Maximum Ground Bounce**

$$V_{gnd-bnc} = p \cdot V_{DD} = \begin{pmatrix} \frac{W_{bus} \cdot L_{11}}{N_g} \end{pmatrix} \begin{pmatrix} \frac{di}{dt} \end{pmatrix} + \sum_{k=2}^{W_{bus}} \begin{pmatrix} M_{1k} \frac{di}{dt} \end{pmatrix}$$

$$\underbrace{Self}_{Contribution} \underbrace{Coupling}_{Contribution}$$

Model Development

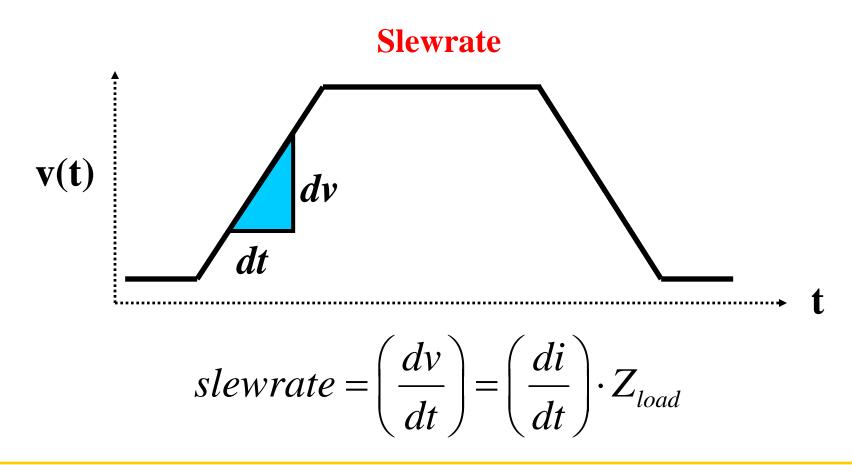

**Maximum Slewrate**

$$\left(\frac{dv}{dt}\right)_{\max} = \frac{p \cdot V_{DD} \cdot Z_{load}}{\left(\frac{W_{bus} \cdot L_{11}}{N_g}\right) + \sum_{k=2}^{W_{bus}} M_{1k}}$$

- pull out (di/dt)

- convert to (dv/dt)

Model Development

**Minimum Risetime**

$$t_{rise-\min} = \frac{\left(0.8\right) \cdot \left[\left(\frac{W_{bus} \cdot L_{11}}{N_g}\right) + \sum_{k=2}^{W_{bus}} \left(M_{1k}\right)\right]}{p \cdot Z_{load}}$$

#### - convert slewrate to risetime

Model Development

**Maximum Datarate**

$$DR_{\max} = \frac{p \cdot Z_{load}}{(1.5) \cdot (0.8) \cdot \left[ \left( \frac{W_{bus} \cdot L_{11}}{N_g} \right) + \sum_{k=2}^{W_{bus}} M_{1k} \right]}$$

- convert Risetime to Datarate

**Maximum Throughput**

$$TP_{\max} = W_{BUS} \cdot DR_{\max}$$

### • **SPICE Simulations were Performed on Three Packages**

**QFP** – Wire Bond

**BGA – Wire Bond**

**BGA – Flip-Chip**

| Package | $L_{11}$ | <i>K</i> <sub>12</sub> | <i>K</i> <sub>13</sub> | $K_{14}$ | <i>K</i> <sub>15</sub> | <i>K</i> <sub>16</sub> | Package | Cost Per-Pin |

|---------|----------|------------------------|------------------------|----------|------------------------|------------------------|---------|--------------|

| QFP-wb  | 4.550n   | 0.744                  | 0.477                  | 0.352    | 0.283                  | 0.263                  | QFP-wb  | \$0.22       |

| BGA-wb  | 3.766n   | 0.537                  | 0.169                  | 0.123    | 0.097                  | 0.078                  | BGA-wb  | \$0.34       |

| BGA-fc  | 1.244n   | 0.630                  | 0.287                  | 0.230    | 0.200                  | 0.175                  | BGA-fc  | \$0.63       |

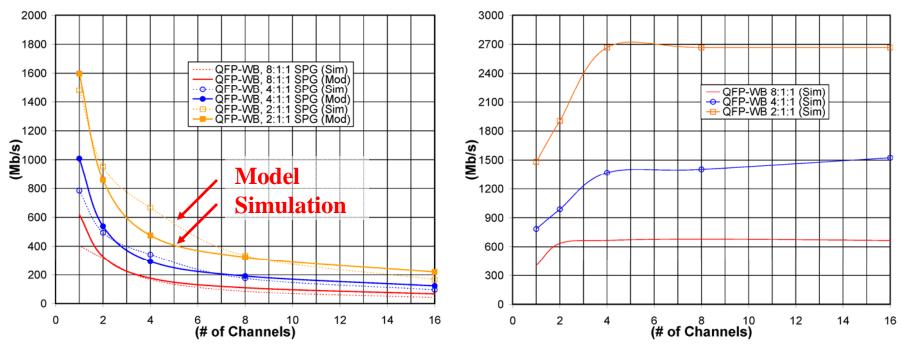

#### • **QFP Wire-Bond Package Simulations**

#### **Per-Pin Data-Rate**

**Bus Throughput**

#### - Throughput reaches an asymptotic limit as channels are added

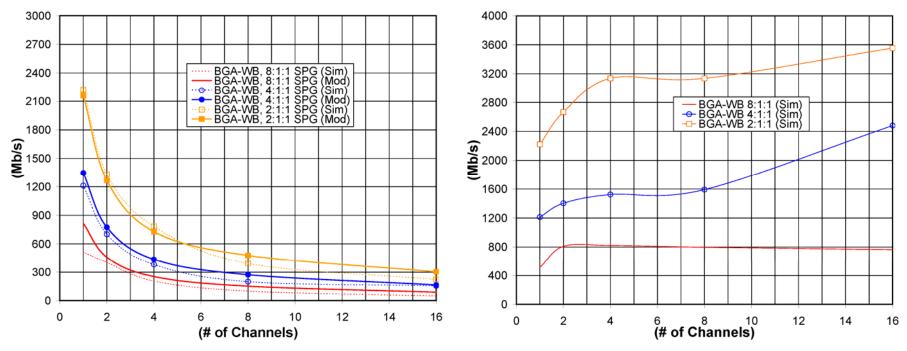

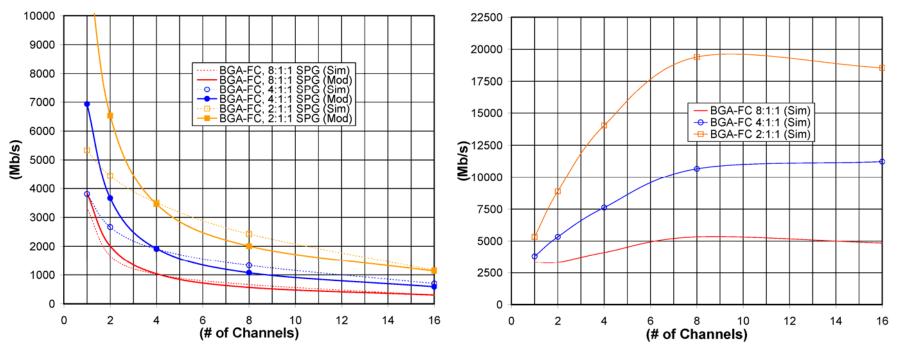

#### • BGA Wire-Bond Package Simulations

#### **Per-Pin Data-Rate**

**Bus Throughput**

#### - Level 1 : BGA Increases Performance Over QFP

### • **BGA Flip-Chip Package Simulations**

#### **Per-Pin Data-Rate**

**Bus Throughput**

- Level 2: Flip-Chip Increases Performance Over Wire-Bond

Cost Must Also Be Considered in Analysis

**Bandwidth Per Cost**

$$BPC = \left(\frac{TP}{Cost_{bus} \cdot 1e^6}\right) \quad \text{Units} = (Mb/\$)$$

• This Metric Represents "Cost Effectiveness of the Bus"

### Bandwidth Per Cost Results

|                   | Number of Channels |      |      |      |     |  |  |  |  |

|-------------------|--------------------|------|------|------|-----|--|--|--|--|

| Bus Configuration | 1                  | 2    | 4    | 8    | 16  |  |  |  |  |

| QFP-WB 8:1:1      | 612                | 722  | 505  | 309  | 152 |  |  |  |  |

| QFP-WB 4:1:1      | 1188               | 1122 | 1036 | 532  | 289 |  |  |  |  |

| QFP-WB 2:1:1      | 2245               | 2165 | 1515 | 758  | 379 |  |  |  |  |

| BGA-WB 8:1:1      | 503                | 594  | 402  | 234  | 112 |  |  |  |  |

| BGA-WB 4:1:1      | 1188               | 1032 | 747  | 390  | 304 |  |  |  |  |

| BGA-WB 2:1:1      | 2179               | 1961 | 1153 | 577  | 327 |  |  |  |  |

| BGA-FC 8:1:1      | 1764               | 1323 | 1085 | 847  | 385 |  |  |  |  |

| BGA-FC 4:1:1      | 2016               | 2116 | 2016 | 1411 | 743 |  |  |  |  |

| BGA-FC 2:1:1      | 2822 🤇             | 3527 | 2785 | 1924 | 920 |  |  |  |  |

#### **Faster Narrower Busses = More Cost Effective**

# **Questions?**